Marinchip 9700 Assembler User Guide by John Walker

(C) Copyright 1978 Marinchip Systems

All Rights Reserved

Revised July 1978

Marinchip Systems Mill Valley, CA 94941 (415) 383-1545

# Table of contents

| J | 1. | Introduction 1.1. Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -5<br>-5                                    |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|   | 2. | Using the assembler 2.1. Calling the assembler 2.2. Assembly listing format 2.2.1. Error flags 2.2.2. Location counter 2.2.3. Object code 2.2.4. Line number 2.2.5. Source code                                                                                                                                                                                                                                                                                                                                                                                   | -2333344<br>-33344                          |

|   | 3. | The assembly language syntax 3.1.1. Labels 3.1.2. Numbers 3.1.3. Strings 3.1.4. Expressions 3.1.4.1. Relocatability 2.1.4.2. Numeric operators 3.1.4.3. Address operators 3.1.4.4. Predefined symbols 3.1.4.5. Programmer-defined symbols 3.1.5. Comments 3.2. Object code linking 3.2.1. External symbol definition 3.2.2. External symbol reference 3.3. Conditional assembly                                                                                                                                                                                   | -4<br>-45<br>-55<br>-67<br>-77<br>-88<br>-8 |

|   | 4. | 4.4. BYTE - Byte generation 4.5. COPY - Copy source file 4.6. DATA - Define 16 bit data 4.7. DORO - Dummy origin 4.8. ELSE - Conditional assembly alternative 4.7. END - End of program 4.10. ENDF - End conditional assembly 4.11. EQU - Define assembly-time variable 4.12. EVEN - Force word alignment 4.13. INT - Identify program                                                                                                                                                                                                                            | -99<br>-1000-1111-1111111111111111111111111 |

|   | 5. | 5.1. Two general address instructions 5.1.1. A — Add words 5.1.2. AB — Add bytes 5.1.3. S — Subtract words 5.1.4. SB — Subtract bytes 5.1.5. C — Compare words 5.1.6. CB — Compare bytes 5.1.7. MOV — Move word 5.1.8. MOVB — Move byte 5.1.9. SOC — Set ones corresponding 5.1.10. SOCB — Set ones corresponding byte 5.1.11. SZC — Set zeroes corresponding 5.1.12. SZCB — Set zeroes corresponding byte 5.2. One general address instructions 5.2.1. B — Branch 5.2.3. BL — Branch and link 5.2.3. BLWP — Branch and load workspace pointer 5.2.4. CLR — Clear |                                             |

#### Table of contents

```

7.8911141

7.8911141

7.8911141

7.8911141

7.8911141

7.8911141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.891141

7.8911

- Negate

MEG

-18

-19

-19

Absolute value

ear

SWPB

- Swap bytes .

-19

-19

INC

Increment

ÎNCT

DEC

- Increment by two

- Decrement

DECT

- Decrement by two

- Execute remote

Х

Register / general address instructions

L. COC -- Compare ones corresponding

- Compare ones corresponding - Compare zeroes corresponding - Exclusive or

GZC

XOR

MPY

- Multiply

טומ

- Divide

Shift instructions

4. 1.

4. 2.

4. 3.

4. 4.

- Shift left arithmetic

- Shift right arithmetic

- Shift right circular

- Shift right logical

SRA

SRA

55.

SRC

Ēki,

5. Immediate operand instructions

5. L. Workspace register immediate

5. L. L. AI — Add immediate

5. L. 2. ANDI — And immediate

5. L. 2. CI — Compare immedia

Workspace register immediate instructions

AI — Add immediate

ANDI — And immediate

-24

-24

-24

5. 1. 2.

5. 1. 5.

5. 2. 1.

5. 2. 1.

5.

5.

CI

LI

- Compare immediate

-25555566477

-2755566477

- Load immediate

- Or immediate

5.

5.

ORI

Internal register immediate instructions

1. LIMI – Load interrupt mask immediate

2. LWPI – Load workspace pointer immediate

5. 5. 2. 1. LIMI — Load interrupt mask in 5. 5. 2. 2. LWPI — Load workspace pointer 5. 6. Jump instructions 5. 6. 1. JMP — Jump unconditional 5. 6. 2. JEQ — Jump equal 5. 6. 3. JNE — Jump not equal 5. 6. 3. JNE — Jump less than 5. 6. 6. JH — Jump high or equal 5. 6. 6. JH — Jump high or equal 5. 6. 7. JNE — Jump high or equal 5. 6. 8. JL — Jump low or equal 5. 6. 9. JLE — Jump low or equal 5. 6. 10. JNC — Jump no carry 5. 6. 11. JNC — Jump no carry 5. 6. 12. JNO — Jump no overflow 5. 6. 13. JOP — Jump od parity 5. 7. Internal register store instructions 5. 7. 2. STWP — Store workspace pointer 5. 8. 1. INLE — Idle processor 5. 8. 1. INLE — Load and restart executions 5. 8. 1. INLE — Load and restart execution 5. 8. 3. RSET — Reset 5. 8. 4. CKON — Clock on 5. 8. 5. CKOF — Clock of 5. 9. Extended operation instruction 5. 9. 1. XOP — Extended operation 5. 10. 1. CRU single bit instructions 5. 10. 1. CRU single bit instruction 5. 10. 10. CRU single bit instruction 5. 10. CRU single bit instruction 5. 10. CRU single bit instruction 5. 10. CRU singl

Control instructions

IDLE - Idle processor

LPEX - Load and restart execution

XDP - Extended operation

Communication register unit (CRU) instructions

5. 10. Co

5. 10. 1.

5. 10. 1. 1.

5. 10. 1. 2.

5. 10. 2. 1.

5. 10. 2. 1.

5. 10. 2. 2.

CRU single bit instructions

SBO — Set bit to one

SBZ — Set bit to zero

TB - Test bit

CRU multiple bit instructions

LDCR - Load communication register

STCR - Store communication register

Pseudo-instructions

a.i. FLOP - Floating operation

b. 2. JSYS - Jump to system

b. 3. NCP - No operation

b. 4. RT - Return

-33

-34

-34

-34

-35

-35

-35

5.

5. 1.

5. 3.

Stack pseudo instructions

DSTK - Define stack pointer

ISTK - Initialise stack pointer

PSHR - Push value on stack

POPR - Pop value from stack

```

ය.

# Table of contents

|    | 6.5.5. POPU - Jump to stack top<br>6.5.6. Example of stack use                                              | -35<br>-35               |

|----|-------------------------------------------------------------------------------------------------------------|--------------------------|

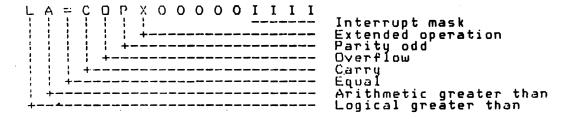

| 7. | Machine reference information 7.1. Instruction summary 7.2. Status register bits 7.3. General address types | -36<br>-36<br>-37<br>-37 |

| 3. | . Sample assembly language program                                                                          | -38                      |

#### 1. Introduction

The Marinchip 9900 Assembler is a relocatable assembler for the Marinchip 9900 computer. It runs on the 9900 computer, accepts source files in a format essentially compatible with the Texas Instruments assembler, and outputs relocatable code completely compatible with T.I. format. The assembler optionally produces an assembly listing, which may be sent to a file or to a printer or console. Lines containing errors will be printed on the user console.

The assembler allows "address expressions", which permit a symbol to be equated to a fully general 9700 address. Such a symbol can be used on instruction fields, and permits the later redefinition of storage use simply by changing the value the symbol was equated to. For example, static storage may easily be changed to storage based on an index register in this manner.

The assembler allows conditional assembly of code depending on assembly-time variables. This allows programs to be easily configured for various code options at assembly time. Conditional code sequences are written with a simple IF - ELSE - ENDF construction, and may be nested to arbitrary depth.

The assembler runs under any Marinchip operating system, and uses the operating system for all its I/O. In addition, since the operating system performs all memory allocation, the assembler automatically uses all configured memory without modification.

#### 1.1. Conventions

In this manual, items which are elements of the language are written in UPPER CASE TYPE. All examples of assembly programs will be in upper case. The assembler itself is insensitive to the case of text, so the programmer need not follow this convention. Items supplied by the programmer will be indicated by Ccorner brackets

, with text inside the brackets describing the item to be coded. Optional items will be enclosed in [square brackets]. The description of the item will make clear what action is taken when specifications are omitted.

#### 2. Using the assembler

#### 2.1. Calling the assembler

The assembler is invoked from operating system command mode by a command of the form:

ASM <reloc>=<source>[,<listing>]

where <reloc> is the name of the file where the relocatable output of the assembly is to be written, <source> is the name of the assembly language program to be assembled, and the optional <listing> is the file where the assembly listing (described below) is written. If the <listing> specification and the comma that precedes it are omitted, the assembler will make no listing, but will print lines on which errors are detected.

For example, to assemble the file MYFILE, place the relocatable object code in file MYOBJ, and send the listing to the file LISTNG, one would use:

ASM MYOBJ=MYFILE, LISTNG

To produce no listing, one would use:

ASM MYOBJ=MYFILE

The files used with the assembler may be either device files or disc files. The listing file, in particular, is frequently sent to the console

or a line printer by specifying the name of that device file.

#### 2.2. Assembly listing format

The assembler optionally generates a listing which includes the source code being assembled and a hexadecimal representation of the object code generated. The format of the listing is explained below.

# 2.2.1. Error flags

If any errors have been detected on this line of the assembly, one or more single-character error flags will be printed which indicate the nature of the error. In some rare cases, the error flag may refer to an error on the line preceding the line on which the flag was printed. The meanings of the flags are as follows:

- D Duplicate. The item in the label field is being redefined. This normally indicates a duplicate label in the program.

- E Expression error. This error indicates an improper expression, or a general syntax error on an instruction or directive.

- I Instruction error. The item in the operation field was not a known instruction or directive.

- Level overflow. An expression was too complicated. It should be rewritten without so many nested parentheses.

- R Relocation error. This generally results from use of a relocatable value when a nonrelocatable value is required, or from an improper mix of relocatable and nonrelocatable values in an expression.

- Truncation. A value was too large for the field in which it had to be placed. For example, using a value greater than 15 when a register number is required will cause this error.

- Undefined. This is not an error, but simply flags a reference to an external symbol. It is issued simply to make external references easier to spot when reading code.

- V Value error. A string or numeric value is too big or badly formed.

- Internal error. This error indicates an internal assembler error. Please submit the source program to Marinchip Systems so that the error may be corrected. PLEASE ALSO SUBMIT ANY FILES INCLUDED BY COPY STATEMENTS IN THE PROGRAM WHICH CAUSED THE ERROR.

The occurrence of any error flag (other than the "U" flag) on a line will cause that line to be printed on the system console, even if the listing has not been requested or is being sent to another file. If the listing is being sent to another file, the error line will be printed both in the listing file and on the system console.

#### 2.2.2. Location counter

If this line generates code, the value of the location counter at the start of the line will be printed. The location counter will be edited as four hexadecimal digits.

# 2.2.3. Object code

If code is generated by the line, it will be printed in hexadecimal cormat. Words will be separated by spaces, and a maximum of three words of code (6 bytes) will be printed on a line. If a line generates more

than three words of code, the code will be continued onto as many additional lines as are required. If a line generates an odd number of bytes, only the actual number of bytes generated will be printed.

# 2.2.4. Line number

The line number of each line in the source program will be printed, followed by a period. If the line being listed is from a COPY file (where listing was specified on the COPY directive), the line number printed will be the line number of the COPY statement in the original program. In this case, the line number will be followed by an asterisk (\*) to identify the code as having come from a COPY file.

#### 2.2.5. Source code

The input source line will be listed exactly as read by the assembler.

# 3. The assembly language

The source language accepted by the assembler consists of two major types of statements: assembler directives and machine instructions. Assembler directives are statements that control the assembler iteslf, and also perform such functions as generation of constant numeric data. Machine instructions are mnemonics for the hardware instructions of the M9900 CPU itself, and are translated into the appropriate binary codes by the assembler and placed in the output file.

# 3.1. Source language syntax

Input to the assembler is written in three major fields, the LABEL field, the OPERATION field, and the OPERAND field. Any information following the operand field is ignored, and may be used for comments. All input is totally free format: information need not be aligned into specific columns. In order to make programs more readable, it is recommended that the operation, operand, and comment fields be aligned. The standard columns used in all Marinchip software are:

| Field                | Columr |

|----------------------|--------|

|                      |        |

| Label                | 1      |

| Operation            | 11     |

| Operation<br>Operand | 21     |

| Comment              | 41     |

If a line has a label, it must start in column one. If column one of a line is blank, it is considered to be an unlabeled line, and the first word on the line is interpreted as an operation.

#### 3.1.1. Labels

All labels defined by the programmer must start with an alphabetic ASCII character, and consist only of alphabetic and numeric characters, or the special character dollar sign (\$). Examples of proper labels are:

# RUNKA BLEEP1 C\$53F1\$ A\$BOOGIE

Examples of improper labels are:

# 6GOBBLE \$ZAP 23SKIDOO

Labels may be up to 80 characters in length, and all characters are significant. The case of alphabetic characters is ignored in comparing labels, so the two labels:

### TESTING and testing

are considered identical by the assembler.

### 3.1.2. Numbers

Numbers accepted by the assembler may be either decimal or hexadecimal. Any number that starts with a leading zero is considered to be hexadecimal, and the characters "A" through "F" are accepted as part of it. Numbers must be less than 65535 decimal, or OFFFF hexadecimal. A sign m generate its two's complement negative representation. The sign is not actually part of the number, as a signed number is considered an expression and evaluated as any other expression: see the section "Expressions" below.

3.1.3. Strings

A string is an arbitrary group of characters enclosed in quote marks. Either single quotes (') or double quotes (") may be used. Strings must be less than 80 characters in length. Two consecutive quotes will cause the second quote to be inserted in the string as a normal character. Hence the string:

'It just ain''t fair.'

will be interpreted by the assembler as the characters:

It just ain't fair.

Strings are used in various contexts by the assembler. A one or two character string may be used wherever a number appears, and has the value of a one or two byte ASCII representation of the quoted characters.

# 3.1.4. Expressions

The element on which the assembler operates is the expression. An expression is composed of numbers, labels, and operators which act on the operands (numbers, labels, and other expressions). An expression may be as simple as a single number, or as complex as imaginable.

Expressions are divided into two major categories: numeric expressions and address expressions. A numeric expression is composed only of nonrelocatable values and numeric operators, while an address expression may contain values with relocation attached, and may be composed through the use of addressing operators. These terms and the distinctions involved should become more clear as the following sections are read.

#### 3.1.4.1. Relocatability

The assembler is capable of generating either relocatable or absolute code for output. Absolute code is able to be loaded for execution only at the address for which it was assembled, but relocatable code is able to be processed for loading at any address by the Linker. In order to allow this, the assembler must, in relocatable code, distinguish between absolute binary values which are not associated with program addresses and hence are invariant, and values which represent program locations and which must be adjusted to reflect the actual address at which the program is loaded. A pure numeric value is referred to as a nonrelocatable quantity, and a program address is referred to as a relocatable quantity. In a typical program, numbers and labels set equal to numbers would be nonrelocatable, while all program labels would be relocatable. To further complicate things, the assembler can also generate absolute code: when in this mode program labels are also absolute.

Because the complete value of a relocatable quantity is not known at assembly time, restrictions are imposed on the operations in which a relocatable quantity may participate. It is legal to:

Add a constant to a relocatable quantity.

- Subtract a constant from a relocatable quantity.

Subtract two relocatable quantities yielding an absolute

- quantity.

4. Compare two relocatable quantities with any of the relational operators.

All other operations will cause an "R" flag (Relocation error) if performed with relocatable quantities.

#### 3.1.4.2. Numeric operators

The numeric operators are as follows:

```

( ) Expression brackets

+ - -- Unary Plus, Minus, NOT

<< >> Shift left, Shift right

Expression brackets

Unary Plus, Minus, NOT

Shift left, Shift right

Logical AND

Logical OR, XOR

Multiply, Divide

Add, Subtract

Equal, Greater, Less

```

The operators are executed in the order given above. For example, in the expression:

A+B\*C

B and C will be multiplied, and the product added to A. This occurs because the "\*" operator has a higher priority than the "+" operator (according to the above table), and hence is executed first. Operators listed in the same line above will be evaluated left to right. Since the parentheses are first in the table, subexpressions within parentheses will always be evaluated first. For example:

(A+B) &C

will cause A and B to be added, and the sum multiplied by C.

The normal arithmetic operators (+, -, \*, and /) operate on 16 bit signed numbers. The division operator (/) discards the remainder from the division. The unary minus operator takes the two's complement negative of its operand (e.g., -A).

The logical operators (++, --, and \*\*) perform bit-by-bit logical operations on their 16 bit operands. The functions performed are OR, XOR, and AND respectively. If the "--" operator is used as a unary operator (e.g., --F), the one's complement negative (inversion of all bits) of the operand will be the result.

The shift operators (<<, >>) logically shift their left operand left or right, respectively, the number of bits in the right operand, modulo 16. For example:

1<<2 is 4 16>>3 is 2

The relational operators (=, >, and <) return 1 if the relation between the two operands is true and zero otherwise. Note that the relational operators can be used with the logical operators to form complex logical expressions.

# 3 1.4.3. Address operators

The address operators are used to build an address value from one or more operands. The form of the address operators are as follows:

The first construction, \*<reg>, causes the expression <reg>, which must be nonrelocatable and have a value between 0 and 15, to be treated as a register which contains the address of an operand.

The second construction, \*<reg>+, is identical to the first, except that following the reference to the register for the address of the operand it will be incremented by the length of the operand (1 if used in a byte instruction, 2 if used in a word instruction).

The third construction, <val>(<reg>), is used to address an operand whose address is the location <val> with the contents of register <reg> added to it. <val> may be any value, relocatable or not, but <reg> must be nonrelocatable and between O and 15.

The fourth construction, @<val>, simply indicates that <val> is to be used as the address of the operand. This is seldom necessary because the assembler automatically generates a direct address for any relocatable operand or absolute operand greater than 15. It is always permissible, though, and required to directly address an absolute address between O and 15

The address operators may be used in any instruction where a "general address" operand is required, and identify the addressing mode to be used with the operand. If none of these operators appear, the mode generated will be the centents of the register of the operand is absolute and between O and 15, and direct otherwise. The address operators may also be used with the EQU directive to equate a simple name to a complex address expression. This can be used to simplify coding and to make programs easier to modify.

#### 3.1.4.4. Predefined symbols

At the start of an assembly, the names for the workspace registers are automatically defined by the assembler. The labels RO through R15 are equated to O through 15.

#### 3.1.4.5. Programmer-defined symbols

Normally, the appearance of a label in column 1 of a line will cause the label to be equated to the current location counter. This is the mechanism by which labels are given to program and data addresses. The EQU (equate) directive allows the programmer to define a label equal to any numeric or address expression. The directive:

<label> EQU <expression>

will set <label> equal to the <expression>. Henceforth in the assembly, the appearance of the <label> will be equivalent to the value of the <expression> at the time the EQU statement was evaluated. Examples of the EQU directive are:

TPORT EQU 020

ALTENT EQU ENTRY+4

STKTOP EQU STACK(R1)

# 3.1.5. Comments

Comments may be placed following the last field evaluated by an instruction or directive. The last field is terminated by a space following the last item, and after that space any sequence of characters may be included as a comment. The assembler will always treat the sequence "period space" (". ") as the end of line, except when it appears inside a quoted string. This convention permits comments to be included on lines where a parameter is omitted (for example, END or RORG), and also allows lines which are all comment. Lines which are to be all comment must have a period space as their first two nonblank characters. The period space may begin in column 1, or some later column. Examples of comments are as follows:

MORE COMMENT

THIS IS A COMMENT RELOCATABLE CODE

Object code linking

The assembler produces relocatable object code which is turned into an executable program by the Linker. The relocatable code allows programs to define labels accessable to other programs, and to reference code and data defined in other assemblies, then combined by the linker into an executable program.

3.2.1. External symbol definition

To define a symbol as an external reference, an asterisk (\*) must follow the appearance of the symbol in the label field. For example, to externally define the entry point to a subroutine, one might code:

ZONK\* MOV

3, 2,

R11, SAVEIT

Save return point

The label ZCNK will be externally defined, and may be referenced by other programs when the Linker is used to produce an executable program. The label ZONK may be referenced within the assembly just like any other non-externally defined label. The format of relocatable code restricts the significance of external symbols to 6 characters. As a result, even though within the assembly labels may be up to 80 characters long and are significant to their full length, externally defined labels must be unique in their first 6 characters.

3.2.2. External symbol reference

An external symbol is referenced simply by using it in the assembly. For example, another program might call the subroutine ZONK defined above with the statement:

BL

ZONK

Zonk the data

An external symbol may appear wherever a 16 bit relocatable quantity may be used. However, an expression such as:

# ZONK+2

is not permitted. An external symbol must be simply used as its defined value (this is a restriction of the relocatable code format). Note that since external symbols are unique only to the first 6 characters, the following symbols:

# BOGGLE BOGGLEKLUNK BOGGLEBARGLE

will all reference the same external symbol, "BOGGLE". Any line which references an external symbol will be flagged with a "U" in the first column of the assembly listing. This is not an error, only an indication that this line references an external symbol.

3.3. Conditional assembly

The assembler allows selection of the code to be assembled based upon the value of assembly-time expressions. This is accomplished through use of the IF, ELSE, and ENDF directives (described in more detail in the "Assembly directives" chapter below). The IF directive takes an expression as an operand. That expression is evaluated, and if nonzero the code following the IF is assembled. If zero, the code between the IF and the matching ENDF will be skipped by the assembler. While skipping code, the assembler will scan for IF and ENDF lines, so that only the ENDF that matches the IF that turned off the assembly will restore the generation of code. This allows IF — ENDF pairs to be nested to any

desired depth. The ELSE directive turns code off if encountered while assembling code, and turns code back on if encountered while skipping code at the outermost IF level. Note that since the IF directive turns code on if its operand is nonzero and off otherwise, and the relational and logical operators follow the convention that I means TRUE and O means FALSE, IF directives may be coded using relational and logical operators with their normal mathematical meaning. Examples of conditional assembly follow:

| MAXMEM<br>SIGNON | EQU<br>:                    | 04000<br>1                                       | Maximum memory size<br>Print Sign-on if nonzero |

|------------------|-----------------------------|--------------------------------------------------|-------------------------------------------------|

| •                | IF<br>JSYS<br>ENDF          | SIGNON<br>PRSIGN                                 | Print sign-on message                           |

|                  | IF                          | SIGNON                                           |                                                 |

| PRSIGN           | BYTE<br>DATA                | WRITE\$,O<br>O,SIGNM,SIGNL,O                     | Packet to print signon                          |

| SIGNM            | TEXT<br>IF<br>TEXT<br>ELSE  | "APL\9900 "<br>MAXMEM>02000<br>"(Large version)" |                                                 |

|                  | TEXT<br>ENDF                | "(Small version)"                                |                                                 |

| SIGNL            | BYTE<br>EQU<br>EVEN<br>ENDF | OD<br>\$-SIGNM                                   | Carriage return<br>Length of message            |

### 4. Assembly directives

Assembly directives are statements in the assembly language that do not correspond to machine instructions. Some of these statements generate data, others simply specify information used by the assembler. A <label> may be specified on any assembly directive. Normally, the <label> will simply be set equal to the value of the location counter prior to processing the directive. In cases where some other action is taken regarding the <label> this will be noted in the description of the directive. The directives are discussed in alphabetical order.

### 4.1. ADRG - Absolute origin

The location counter is set to the value of <expression> and the assembler begins generating absolute code. Absolute code is not relocated by the Linker, so data generated following the AORG directive will be placed starting at the address specified by <expression>, regardless of where the program is loaded. If a <label> is specified, it will be set equal to the new location counter following the processing of the AORG directive.

# 4.2. BES - Block ending with symbol

<label> BES <expression>

The number of bytes indicated by <expression> will be reserved by adding the <expression> to the location counter. The <label> will be set equal to the first address following the reserved area. This directive is used for reserving tables which are addressed in order of descending address. For example, if the location counter were at O200 and the directive:

STACK DES 040

were processed, the label STACK would be set equal to 0240.

4.3. BSS - Block starting with symbol

<label> DSS <expression>

A block of storage with the length in bytes specified by <expression> is reserved by adding <expression> to the location counter. If a <label> is specified, it is set to the address of the first byte of the block reserved. This is the normal means by which blocks of memory are reserved.

4. 4. BYTE - Bute generation

<label> BYTE <expression>, Cexpression>, ...

Each Cexpression

specified is output in a single byte of data. If the Cexpression

is relocatable or has a value greater than 255 a truncation error will be flagged. Any number of bytes may be generated by specifying multiple expressions.

4.5. COPY - Copy source file

The distrings specifies the name of a file. That file is read and included in the assembly. Text from the file is processed as if it came from the file being assembled, except that it is not listed unless the dexpressions is specified and has a nonzero value. The COPY directive is normally used to include common definitions or frequently used pieces of code in multiple assemblies without the need for physically including the code in each assembly.

)

4.6. DATA - Define 16 bit data

<label> DATA <expression>, Cexpression>, . .

The DATA directive generates one 16 bit word for each Cexpression>

specified. The Cexpressions> may be either relocatable or nonrelocatable.

4.7. DORG - Dummy origin

<label> DORG <expression>

The DCRG directive sets the location counter to the absolute value specified by <expression>, places the assembler in absolute mode, and turns off the actual generation of code. DCRG is most often used when defining data structures. A "DCRG O" directive can be used to turn on dummy assembly and set the location counter to zero. The components of a data structure can then be reserved by BSS directives, and then normal assembly can be resumed with an ACRG or RCRG directive. This allows use of the assembler to allocate storage within a data structure without explicit definition by the programmer. If a <label> is specified, it will be set equal to the new location counter value, in other words, to <expression>.

SE = Conditional assembly alternative

<label> ELSE

When the ELSE directive is encountered, and the IF nesting level is one (indicating that the outermost IF is in effect), if code was turned off by the IF it is turned back on. If the code was turned on by the IF, the ELSE turns it off. This allows alternate code to be generated by the sequence: IF - ELSE - ENDF.

# 4.9. END - End of program

<label> END [<expression>]

The END directive identifies the end of an assembly and must be the final line in any file to be assembled. If no <expression> is specified as an operand, the program will be generated with no starting address specified. If an <expression> is specified, a starting address will be generated, making this a main program. The <expression> will normally simply be the label on the line containing the first instruction to be executed in the program.

#### 4.10. ENDF - End conditional assembly

#### <label> ENDF

If encountered while skipping code because of an IF or ELSE directive, the IF nesting is decremented. If zero, indicating that the ENDF matches the IF or ELSE that turned off the processing of code, the assembly resumes with the next line. If nonzero, this ENDF matches an IF within a region of code turned off by an outer IF, and the nesting level is simply decremented. If the ENDF is encountered during normal assembly, it is simply ignored, since the block of code it terminates was turned on.

4.11. EQU - Define assembly-time variable

# <label> EQU <expression>

The <label> is set equal to the value of the <expression> and may be used henceforth in the assembly to represent the value of the <expression>. The <expression> may be either a numeric or address expression, and may be either relocatable or nonrelocatable (subsequent use of the label, of course, may occur only in a context where the <expression> itself would be permissible). A <label> may be redefined at any time by an EQU statement.

4.12. EVEN - Force word alignment

#### <label> EVEN

If the location counter is odd, one byte will be reserved to force it to be even. This directive is normally used following a block of BYTE or TEXT data, or byte-aligned blocks reserved by BSS or BES, to insure that the location counter is at a word boundary before generating instructions or data which require word alignment.

4.13. 1DT - Identify program

####

The program identification is set equal to the <string> specified. The program identification may be up to 8 characters in length, and is printed by the Linker when a memory map is requested. If no IDT statement is supplied in the program, the value "NO IDT!" will be used.

4.14. IF - Conditional assembly

#### Clabel> IF <a href="mailto:cexpression"></a>.

The <expression>, which must be a nonrelocatable quantity, is evaluated. If nonzero, the IF directive is ignored and the assembly continues normally. If zero, the assembler skips all subsequent lines until a matching ELSE or ENDF directive is found. While skipping code, the assembler will scan for IF and ENDF directives so that nested IF - ENDF equences will be correctly processed. Lines skipped by an IF directive

will be listed in the output listing (if one is being generated), but no  ${\mathfrak F}$  code will be assembled for them.

4.15. LIST - Enable assembly listing

<lase10 LIST</pre>

If the assembly listing has been suppressed by a preceding UNL directive, it will be resumed.

4.16. PAGE - Eject page in assembly listing

<labelD: PAGE</pre>

If an assembly listing is being generated, a page eject will occur following the line containing the PAGE directive. This may be used to cause separate pieces of a program to be listed on separate pages.

4 17. RORG - Relocatable origin

The RDRG directive sets the assembler producing relocatable code, and sets the relocatable location counter to the value of <expression>. If <expression> is omitted, the location counter will be set to the length of all relocatable code previously generated in the program. This is useful to return to relocatable code generation following an absolute block (ADRG) or dummy block (DDRG). When an assembly starts, the assembler assumes a:

RORG (

directive is in effect. If a <label> is specified, it will be set equal to the value of the location counter following processing of the RORG directive.

4 18. TEXT - Generate character data

<label> TEXT [-]<string>

The TEXT directive generates bytes containing the ASCII character codes for each character in a <a href="String">String</a>. If the <a href="String">String</a> is preceded by a minus sign, the two's complement of the final character will be generated (to serve as an end of string indication). Note that TEXT generates only as many bytes as there are characters in the string, and that as a result and odd number of bytes may be generated. If the data following the TEXT directive must be aligned on word boundaries, an EVEN directive should follow the TEXT line.

4.19. TITL - Title for assembly

Clabell TITL (string)

The TITL directive specifies a title to be printed on each page of the assembly listing. The  $\langle strinq \rangle$  will be printed at the head of each page of the assembly listing until the end of the assembly or until superceded by another TITL directive.

4.20. UNL. - Turn off assembly listing

Clabel > UNL

The assembly listing will be suppressed. The listing may be later

resumed, if desired, by a LIST directive.

# 5. Instruction descriptions

The following sections describe the machine instructions of the M9900 CPU, giving the symbolic assembler syntax used to generate each instruction. The instructions are grouped by general type: each instruction within a type shares a common syntax with all others of the same type.

Within the instruction descriptions, the following nomenclature will be used for items supplied by the programmer when coding an instruction:

In coding these fields, any address expression may be used for a general address (Agas) or (Agad). A workspace register address must be a nonrelocatable expression between 0 and 15. An immediate operand may be a relocatable or nonrelocatable value, but may not be an address expression. A (destination) address is a value whose relocation must be the same as the code currently being generated. A (count) must be nonrelocatable and between 0 and 16, and an (index) must be nonrelocatable and between 0 and 15.

# 5.1. Two general address instructions

The two general address instructions take two general address operands. The first is referred to as the "source", and the second is referred to as the "destination". The instruction normally operates upon the two operands and stores its result, if any, into the destination.

#### 5. 1. 1. A - Add words

A <gas>، <gad>

The source operand word is added to the destination operand and the result is stored into the destination operand. The result is compared against zero and the condition bits are set accordingly. If there is a carry out of the add, the carry bit is set, and if the result cannot be represented as a 16 bit integer, the overflow flag is set.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Op code: A000

Format: 11010ttddddttssss

Destination Source

5. 1. 2. AB — Add bytes

AB (gas>, <gad>

The source bute operand is added to the destination bute operand and the result is stored into the destination bute operand. When the source or destination operand is a workspace register, the bute addressed will be the upper bute in the register (bits 15 - 8). The other bute in the destination address will be unchanged. The result of the addition is compared to zero and the status bits are set accordingly. If there is a carry out of the butes added, the carry bit will be set, and if the result of the addition is not representable as an 8 bit two's complement integer,

the overflow bit will be set. The parity status bit is set when the number of bits in the result is odd, and is cleared otherwise.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow, parity.

Op code: BOOO

Format:

1011ttddddttsss

Destination Source

5. 1. 3. S

- Subtract words

S <gas>/<gad>

The source operand is subtracted from the destination operand and the result is stored in the destination operand. The result is compared with zero and the status bits are set resulting from the operation. When there is a carry out of the most significant bit, the carry bit is set, and when the difference cannot be represented as a 16 bit integer, the overflow bit is set.

Status bits affected; Logical greater than, arithmetic greater than, equal, carry, overflow.

Op. code: 6000

Format:

OllOttddddttsss

Destination

Source

5. 1. 4. SB

- Subtract bytes

SB

<gas>, <gad>

The source bute operand is subtracted from the destination byte operand. The result is stored in the destination byte operand. The result is compared with zero and the status bits are set accordingly. If there is a carry out of the most significant bit of the byte, the carry bit will be set, and if the difference cannot be represented as an 8 bit integer, the overflow bit will be set. If there are an odd number of one bits in the result bute, the parity status bit will be set, otherwise the odd parity status bit will be cleared. If either the source or destination operand is a workspace register, the high byte (bits 15-8) will be used as the operand. The other byte in the word containing the destination operand will not be changed by this instruction.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow, parity.

Op code: 7000

Format:

Ollittddddttsss

Destination Source

5.1.5. C

- Compare words

C

<gas>, <gad>

The source operand is compared to the destination operand and the status bits are set as a result of the comparison. The arithmetic greater bit is set if the source operand is greater than the destination when both are considered as 16 bit two's complement integers. The logical greater bit is set if the source operand is greater than the destination operand when both are considered as 16 bit unsigned numbers. The equal bit is set if the two operands are bit-for-bit equal.

| Status bits affectequal.                                                                                            | ted: Logical                                              | greater than,                                                      | arithmetic                                                   | greater than,                                        |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|

| Op code: 3000                                                                                                       |                                                           |                                                                    |                                                              |                                                      |

| Format: 1000ttdd                                                                                                    |                                                           |                                                                    |                                                              |                                                      |

|                                                                                                                     | Sout                                                      | tination<br>rce                                                    | -                                                            |                                                      |

| 5. 1. 6. CB - (                                                                                                     | Compare bytes                                             |                                                                    |                                                              |                                                      |

| •                                                                                                                   |                                                           |                                                                    |                                                              |                                                      |

|                                                                                                                     | <gas>,<gad></gad></gas>                                   |                                                                    |                                                              |                                                      |

| The source byte operarithmetic greater described above for considered as 8 addition, the parity number of one bits. | than logical                                              | annatan than                                                       | and cours hi                                                 | te 220 cot 20                                        |

| Status bits affectequal, parity.                                                                                    | ted: Logical                                              | greater than,                                                      | arithmetic                                                   | greater than,                                        |

| Op code: 9000                                                                                                       |                                                           |                                                                    |                                                              |                                                      |

| Format: 1001ttdd                                                                                                    |                                                           | *:*:                                                               |                                                              |                                                      |

| <del></del> -                                                                                                       | Sou                                                       | tination<br>rce                                                    |                                                              |                                                      |

| 5. 1. 7. MOV -                                                                                                      | Mave word                                                 |                                                                    |                                                              |                                                      |

| MOV                                                                                                                 | <gas>, <gad></gad></gas>                                  | •                                                                  |                                                              |                                                      |

| The source operand with zero and the s                                                                              | is moved to the<br>tatus bits are                         | destination.<br>set as a result                                    | The result of the comp                                       | is compared<br>arison.                               |

| Status bits affec                                                                                                   | ted: Logical                                              | greater than,                                                      | arithmetic                                                   | greater than,                                        |

| Opcode: C000                                                                                                        |                                                           |                                                                    |                                                              |                                                      |

| Format: 1100ttdd                                                                                                    |                                                           | tination<br>rce                                                    |                                                              | ·                                                    |

| 5.1.8. MOVB -                                                                                                       | rio∨e byte                                                |                                                                    |                                                              |                                                      |

| J. 1. B. HUVD -                                                                                                     | nove byte                                                 |                                                                    |                                                              |                                                      |

| MOVB                                                                                                                | <gas>, <gad></gad></gas>                                  |                                                                    |                                                              |                                                      |

| The source byte ope in the destinatio workspace register, byte moved is coresult of the compabits, the parity bi    | n is unaffect the upper byte mpared against rison. If the | ed. If the s<br>(bits 15-8) was zero and the co<br>byte moved cont | source or des<br>vill be add<br>andition bits<br>ains an odd | tination is a ressed. The are set as a number of one |

| Status bits affec<br>equal, parity.                                                                                 | ted: Logical                                              | greater than,                                                      | arithmetic                                                   | greater than,                                        |

| Op code: DOOO                                                                                                       |                                                           |                                                                    |                                                              | ^                                                    |

| Format: 1101ttdd                                                                                                    | _                                                         |                                                                    |                                                              |                                                      |

| 100 Feb 100                                                                                                         |                                                           | tination<br>rce                                                    | •                                                            | -                                                    |

5.1.9. SUC - Set ones corresponding

<qas>, <qad>

For each one bit in the source operand.

destination operand is set to one. Bits in the destination correspond to zero bits in the source will be unchanged. The rescompared to zero and the status bits are set accordingly.

compared to zero and the status of the source will be unchanged. the corresponding bit in Bits in the destination in that The result is ordingly. This with the destination.

Status bits affected: Logical greater than, arithmetic greater than, equal.

Op code: E000

Format:

111Ottddddttssss

Destination

Source

5.1.10. SOCB - Set ones corresponding byte

> SOCB -<gas>, <gad>

For each one bit in the byte source operand, the corresponding bit in the destination byte operand is set to one. Bits in the destination that correspond to zero bits in the source will be unchanged, as will the other byte in the destination word. If the source or destination operand are workspace registers, the upper byte (bits 15-8) will be used as the operand. The result byte is compared to zero and the status bits are set accordingly. If the result byte has an odd number of one bits, the parity bit will be set, and cleared otherwise. This instruction is equivalent to a logical OR of the source and destination bytes.

Status bits affected: Logical than, arithmetic greater than, greater equal, parity.

Op code: F000

1111ttddddttsss Format:

Destination

Source

5. 1. 11. SZC - Set zeroes corresponding

> SZC <gas>、<gad>

For each one bit in the source operand, the corresponding bit in the destination operand is cleared to zero. Bits corresponding to bits in the source operand will be unchanged. The result of the operation will be compared to zero and the status bits will be set accordingly. This For AND equivalent to an with the one's complement of the instruction is source operand.

arithmetic greater than, Status bits affected: Logical greater than, equal.

4000 Op code:

Format: 0100ttddddttsss

Destination

Source

5. 1. 12. SZCB - Set zeroes corresponding byte

> SZCB <gas>、<gad>

For each one bit in the source byte operand, the corresponding bit in the

destination byte operand will be cleared to zero. Bits in the destination that correspond to zero bits in the source will be unchanged, as will be the other byte in the destination word. The result byte will be compared to zero and the status bits will be set according to the result of the comparison. If the result byte contains an odd number of one bits, the parity bit will be set, otherwise it will be cleared. If the source or destination operands are workspace registers, the byte addressed will be the upper byte (bits 15-8).

Status bits affected: Logical greater than, arithmetic greater than, equal, parity.

Op code: 5000

Format: 0101ttddddttssss

---- Destination

Source

5.2. One general address instructions

The one general address instructions contain a single general address specification. The source operand is obtained from this address and the result, if any, is stored back at the same address.

5. 2. 1. B - Branch

B <ga>>

The program counter is set equal to the address to which the general address evaluates. Execution will continue at that address.

Status bits affected: none.

Op code: 0440

Format: 0000010001ttdddd

Destination

5.2.2. DL. - Branch and link

BL <qa>

Workspace register 11 (R11) is set equal to the address following the BL instruction, and the program counter is set equal to the address to which the general address  $\langle ga \rangle$  evaluates. This is the normal subroutine call instruction.

Status bits affected: none.

Op code: 0680

Format: 0000011010ttdddd

Destination

5. 2. 3. BLWP -- Branch and load workspace pointer

BLUP <ga>

The workspace pointer is set equal to the word at the address designated by <ga>, and the program counter is loaded with the contents of the following word. Within the new workspace, register R13 is set equal to the previous workspace pointer, R14 is set equal to the address following the BLWP instruction, and R15 is set equal to the status register. This instruction enters a subroutine which operates with a different register set. The loading of the calling context into the registers of the new workspace permits the subroutine to return simply by executing a RTWP instruction.

Status bits affected: none. 0400 Op code: 0000010000ttdddd Format: Destination 5. 2. 4. CLR - Clear CLR <qa> The word at address <ga> is cleared to zero. Status bits affected: none. 04C0 Op code: 0000010011ttdddd Format: Destination 5, 2, 5, SETO - Set to all ones SETO <ga>> The word at address  $\langle ga \rangle$  is set to all ones (OFFFF). Status bits affected: none. Op code: 0700 0000011100ttdddd Format: Destination 5. 2. 5. TNV - Invert INV <ga>> The word at address <ga> is one's complemented. That is, are set to one and all one bits are set to zero. The result to zero and the status bits are set accordingly. That is, all zero bits i s bits affected: Logical greater than, arithmetic greater than, Status equal. 0540 Op code: الرز 0000010101ttdddd Format: Destination 5. 2. 7. MEG - Negate MEQ <ga>> The word at address (ga) is negated (two's complement negative). This is accomplished by inverting all bits of the operand and then adding one. The result of the negation is compared to zero and the status bits are set accordingly. In two's complement representation there is one more negative number than there are positive numbers. The number -32768, hexadecimal 08000, has no positive counterpart. An attempt to negate this number will set the overflow status bit. Status bits affected: equal, carry, overflow. Logical greater than, arithmetic greater than, Op code: 0500 Format: 0000010100ttdddd 18

Destination

5.2.8. ABS - Absolute value

ABS <ga>

The absolute value of the operand at <ga> is taken and stored back at <ga> The absolute value is taken by examining the sign bit of the operand. If zero, the operand is left unchanged. If one, the operand is two's complemented. The original operand is compared against zero and the status bits are set accordingly. If the original operand is -32768 (08000 hexadecimal), a negative number which has no positive counterpart, the overflow status bit will be set.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Op code: 0740

Format: 0000011101ttdddd

Destination

5. 2. 9. SMPB - Swap bytes

SWPB <ga>

The most significant and least significant bytes of the operand at <ga>are exchanged. The result is equivalent to shifting the source operand circularly 8 bits.

Status bits affected: none.

Op code: 0600

Format: 0000011011ttdddd

----- Destination

5. 2. 10. INC - Increment

INC <ga>.

The value at  $\leq ga >$  is incremented by one. The result is compared to zero and the status bits are set accordingly. If a carry out or overflow occurs, the status bits will be set to reflect it.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Op code: 0580

Format: 0000010110ttdddd

Destination

5. 2. 11. INCT - Increment by two

INCT <ga>

The value at  $\langle ga \rangle$  is incremented by two. The result is compared to zero and the status bits are set accordingly. If a carry out or overflow occurs, the status bits will be set to reflect it.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Jp code: 0500

Format: 0000010111ttdddd

Destination

5. 2. 12. DEC - Decrement

DEC (ga)

The value at  $\leq\!\!ga\!>$  is decremented by one. The result is compared to zero and the status bits are set accordingly. If a carry out or overflow occurs the status bits will be set to reflect it.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Op code: 0500

Format: 0000011000ttdddd

Destination

5. 2. 13. DECT - Decrement by two

DECT <ga>

The value at  $\langle ga \rangle$  is decremented by two. The result is compared to zero and the status bits are set accordingly. If a carry out or overflow occurs the status bits will be set to reflect it.

Status bits affected: Logical greater than, arithmetic greater than, equal, carry, overflow.

Op code: 0640

Format: 0000011001ttdddd

Destination

5 2.14. X - Execute remote

X <ga>

The word at <ga> will be used as the operation code of the current instruction. In other words, the X instruction causes the instruction at the specified address to be executed. The program counter is not changed, however, so execution will continue in line following the X instruction (assuming that the instruction executed does not itself change the program counter). There are several wrinkles associated with this instruction. First, if the instruction executed requires data words following it for immediate data or direct addresses, these words will be loaded following the X instruction, not following the address executed. Second, if the instruction executed is a relative jump instruction, the displacement will be added to the address of the X instruction, not the address of the instruction; this is seldom what the programmer had in mind. Third, the hardware instruction fetch signal is not turned on when the operand of the X instruction is fetched. This may confuse some user implemented special purpose hardware that counts on this signal. Fourth, while the X instruction itself changes no status bits, the instruction executed will set the status bits as it normally would:

Status bits affected: none, however instruction executed will set status bits normally.

Op code: 0480

Format: 0000010010ttdddd

Destination

# 5.3. Register / general address instructions

These instructions take their source operand from the general address specified in the instruction, and use a workspace register specified in the instruction as the destination operand.

5.3.1. COC - Compare ones corresponding

CDC <gas>, <wa>

The contents of the workspace register (wa) are tested against the contents of the general address (gas). If every bit which is a one in (gas) is also a one in (wa), the equal status bit is set. Otherwise (if one or more bits in (gas) which are ones correspond to zero bits in (wa) the equal status bit is cleared. This instruction is most often used where the workspace register contains a set of bits indicating logical values, and the general address operand is a word containing a single bit denoting one of those values. The COC instruction permits a simple test for whether that bit is set in the workspace register. COC can, of course, also be used to test multiple bits for being set.

Status bits affected: Equal.

Op code: 2000

Format: 001000wwwwttssss

Workspace register Source

50000

5. 3. 2. CZC - Compare zeroes corresponding

CZC <gas>, <wa>

The contents of the workspace register (wa) are tested against the contents of the general address (gas). If for every position in (gas) which is a one bit, the corresponding bit in (wa) is a zero, the equal status bit is set. Otherwise (one or more bits which are ones in (gas) correspond to zero bits in (wa), the equal status bit is cleared. This instruction can be used similarly to COC to test whether a single bit is off, and is particularly useful to test whether a field of bits are all zero.

Status bits affected: Equal.

Op code: 2400

Format: 001001wwwwttssss

Workspace register Source

5.3.3. XOR - Exclusive or

XOR <gas>,<wa>

The contents of the general address operand <gas> and the workspace register <wa> are bit-by-bit exclusive ored, and the result is stored in the workspace register <wa>. The result is compared against zero and the status bits are set accordingly.

Status bits affected: Logical greater than, arithmetic greater than, equal.

Op code: 2800

Format: 001010wwwwwttssss

Workspace register destination Source

5.3.4. MPY - Multiply

MPY <gas>, <wa>

The contents of the general address operand <gas> and the workspace register <wa>> are multiplied as two unsigned 16 bit quantities. The 32 bit product is stored with the high-order 16 bits in the workspace register <wa>> and the low order 16 bits in the next higher register (if <wa>> is R15, the low order word will be stored in the next word in memory following the current workspace register set). Note that this instruction performs UNSIGNED multiplication, and hence if used with two's complement numbers will produce incorrect results. If used with signed quantities, user code must handle the sign. This instruction changes no status bits.

Status bits affected: none.

Op code: 3800

Format: 001110wwwwttssss

Workspace register destination

Source

5. 3. 5. DIV - Divide

DIV <gas>, <wa>

The 32 bit quantity with the high order 16 bits in workspace register <wa> and the low order 16 bits in the next consecutive memory location is divided by the 16 bit contents of the general address operand <gas>. The division is done treating both operands as unsigned numbers. The quotient from the division is stored in workspace register <wa>, and the remainder is stored in the next consecutive memory location (which will be the next higher register unless <wa> is R15</a>). If the quotient from the division would exceed 65535 (OFFFF hexadecimal), the operation will be aborted and the overflow status bit will be set.

Status bits affected: Overflow.

Op code: 3COO

Format: 001111wwwwttssss

Workspace register destination

Source

5.4. Shift instructions

The shift instructions shift the contents of a workspace register in various manners. The number of bits to shift is determined in the following manner: each shift instruction contains a four bit "shift count" field. If that field is nonzero, the shift instruction shifts that number of bits. If the shift count field is zero, the low-order 4 bits of workspace register O (RO) are used for shift count. If the low-order 4 bits of RO are zero, the shift will be 16 bits, otherwise the shift will be the number represented by the low 4 bits of RO.

5. 4. 1. SLA - Shift left arithmetic

SLA <wa>><count>

The contents of the workspace register <wa> are shifted left by the specified number of bits, and the result is stored back in <wa>. Vacated bit positions on the right are filled with zeroes. If the sign bit of the operand changes during the operation, the overflow status bit will be set. The value of the last bit shifted out will be placed in the carry status bit. The result is compared to zero and the status bits are set accordingly.

Status bits affected: Logical greater than, arithmetic greater than,

|             | equal, c                                                                        | arry, o                                                                                     | ∕erflow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                      |                                | i                                                           |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |